# Large Q-Factor Improvement for Spiral Inductors on Silicon Using Proton Implantation

K. T. Chan, C. H. Huang, Albert Chin, *Senior Member, IEEE*, M. F. Li, *Senior Member, IEEE*, Dim-Lee Kwong, *Senior Member, IEEE*, S. P. McAlister, *Senior Member, IEEE*, D. S. Duh, and W. J. Lin

**Abstract**—We have improved the Q-factor of a 4.6 nH spiral inductor, fabricated on a standard Si substrate, by more than 60%, by using an optimized proton implantation process. The inductor was fabricated in a 1-poly-6-metal process, and implanted after processing. The implantation increased the substrate impedance by  $\sim$  one order of magnitude without disturbing the inductor value before resonance. The S-parameters were well described by an equivalent circuit model. The significantly improved inductor performance and VLSI-compatible process makes the proton implantation suitable for high performance RF ICs.

**Index Terms**—Implantation, inductor, Q-factor, RF.

## I. INTRODUCTION

SILICON technology supports the needs of the rapidly growing communication market because of its low cost, high package density and mature technology. The widely used inductors on Si wafers, especially those for impedance matching and LC tanks in RF CMOS circuits, have poor quality (Q)-factors. This is mainly due to the high substrate RF loss of the low resistivity ( $10 \Omega\text{-cm}$ ) Si wafers [1]–[9] and the ohmic loss of the spiral metal. Since the ohmic loss can be reduced by using thick metal lines and highly conductive copper, the substrate loss becomes the dominant factor for the inductor's Q-factor. Several methods have been proposed to overcome this problem, such as isolating the substrate by using a thick dielectric layer [1] or a MEMS-etched air-gap below the inductors [2]. However, these nonconventional VLSI processes require additional process steps and package costs. In this paper, we have successfully improved the inductor's Q-factor using an optimized proton implantation process compatible with current VLSI technology [4]–[6]. The ion implantation process [3]–[9] is implemented after device fabrication and transforms the standard  $10 \Omega\text{-cm}$  Si substrate into high resistivity ( $\sim 10^6 \Omega\text{-cm}$ ) material [6] similar to semi-insulating

Manuscript received March 5, 2003; revised July 16, 2003. This work was supported by the NSC under Grant 91-2215-E-009-038 and the NRC-NSC Collaborative Program. The review of this letter was arranged by Associate Editor Dr. Arvind Sharma.

K. T. Chan, C. H. Huang, and A. Chin are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

M. F. Li is with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore, 119260.

D.-L. Kwong is with the Department of Electrical and Computer Engineering, The University of Texas, Austin, TX 78752 USA.

S. P. McAlister is with the National Research Council of Canada, Ottawa, ON, Canada.

D. S. Duh and W. J. Lin are with the Institute of Nuclear Energy Research, Taoyuan, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LMWC.2003.819383

GaAs. The process enhanced the Q-factor by 61% without changing the inductance value, which demonstrates the benefits of using this simple VLSI-compatible implantation process.

## II. EXPERIMENTAL PROCEDURE

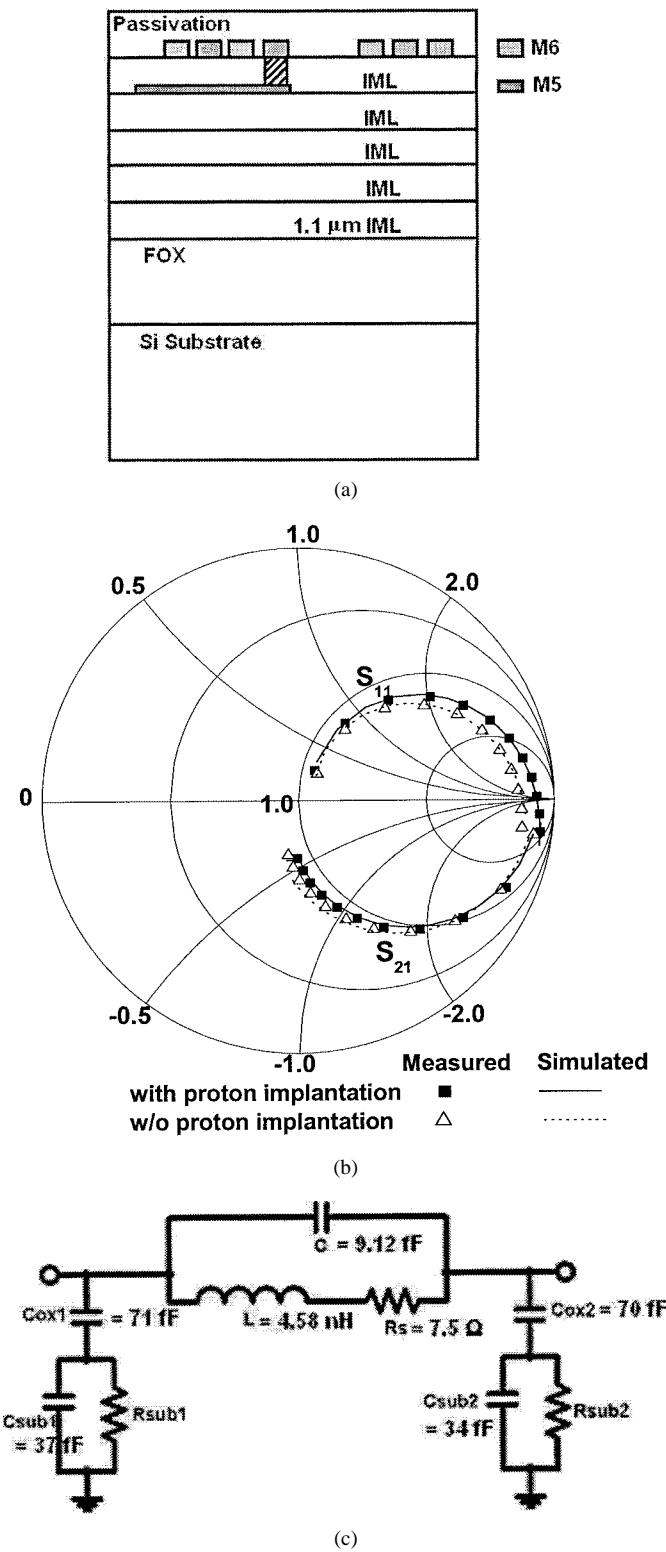

A conventional standard  $0.18 \mu\text{m}$  1-Poly-6-Metal (1P6M) Al-SiO<sub>2</sub> CMOS technology was used to fabricate the inductors and the simplified cross section is shown in Fig. 1(a). The substrate was the standard low-resistivity  $\sim 10 \Omega\text{-cm}$  Si wafers used in a conventional CMOS process. The last metal (M6) is  $2 \mu\text{m}$  thick which reduces the metal ohmic loss of the spiral inductor, while the thickness of other metal layers is  $0.5 \mu\text{m}$ . Each inter-metal layer (IML) thickness is  $1.1 \mu\text{m}$  which is composed of two dielectric layers with dielectric constants of 3.7 and 4.2. The spiral inductor has 3.5 turns and a  $166 \mu\text{m}$  inner diameter with a line width of  $10 \mu\text{m}$  and a spacing of  $5 \mu\text{m}$ . After fabrication the inductors, a proton implantation process was applied with energy of  $\sim 4 \text{ MeV}$  from a synchrotron ion source [3]–[9]. Compared with our previous implantation scheme, which was applied before device fabrication [3]–[9], the present approach, performed after full wafer fabrication, avoid any contamination to the VLSI process line. We measured the RF performance of the inductors with HP8510C Network Analyzer and performed standard de-embedding to remove the parasites associated with the pads.

## III. RESULTS AND DISCUSSIONS

Fig. 1(b) shows the measured and modeled S-parameters for RF inductor fabricated using 1P6M process, where the modeled data is from the equivalent circuit and extracted values shown in Fig. 1(c). The slightly different S-parameters after implantation are due to the reduction of substrate impedance as explained by the equivalent circuit model analysis later. The inductor model consists of a series inductor L, series resistor R<sub>s</sub> and a parallel capacitance C from the capacitive coupling of spiral turns. The C<sub>ox1</sub> and C<sub>ox2</sub> represent the capacitors from isolation oxide underneath the inductor, which include both inter-metal dielectric and trench isolation oxide. The C<sub>sub</sub> and R<sub>sub</sub> represent the RF loss path to ground. Except the substrate resistance (R<sub>sub</sub>), the component values in the models are almost the same for inductors with and without proton implantation. Good agreement between measured and modeled S-parameters is obtained for the inductors with or without the proton implantation, indicating the accuracy of the physically-based circuit model that can also be used for substrate loss analysis.

Fig. 1. (a) Simplified cross section of spiral inductors using 1P6M Al-SiO<sub>2</sub> CMOS Technology. (b) The simulated and measured S-parameters up to 10 GHz, for inductors with and without the proton implantation. (c) The equivalent circuit model with component values for the inductors.

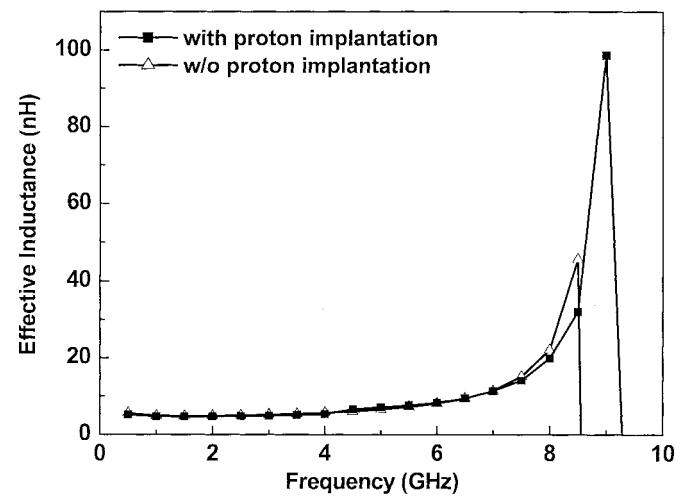

Fig. 2 shows the deduced inductance from the measured de-embedded S-parameters [10]–[12] with or without the proton implantation. The inductance of 4.6 nH is the same for both cases indicating that the proton implantation has almost no influences on the inductance value over a large frequency range.

Fig. 2. Inductance values with and without the proton implantation.

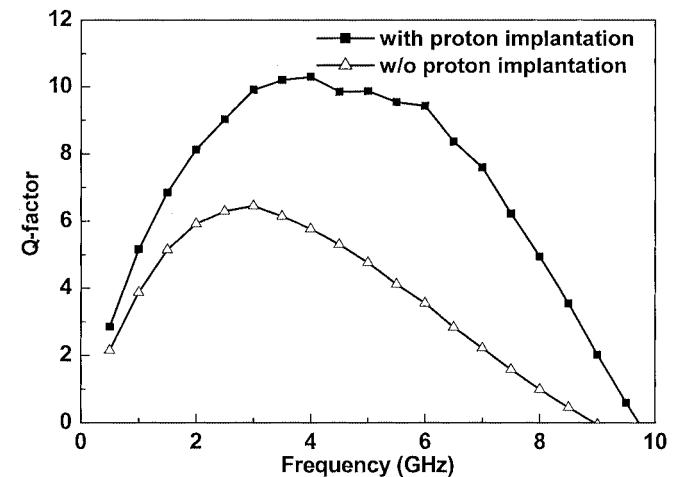

Fig. 3. Q-factor for the inductors, with and without the proton implantation.

This suggests that the proton implantation does not disturb the magnetic field around the inductor, up to at least 7 GHz, before self-resonance [13], [14]. Following implantation, the self-resonant frequency was  $\sim 9$  GHz, which is 7% higher than the original value.

Fig. 3 shows the Q-factors for the inductor with and without the proton implantation. The inductor without the implantation has the max. Q-factor of 6.3 at 3 GHz, whereas the proton-implanted device peaks at 4 GHz with a Q-factor of 10.6. In addition to the 61% peak Q-factor improvement, the high Q-factor region is simultaneously extended to 6.2 GHz by using the using implantation process. This broader high Q-factor frequency region enables the 4.6 nH inductor to be useful for Wireless LAN (5.2–5.8 GHz).

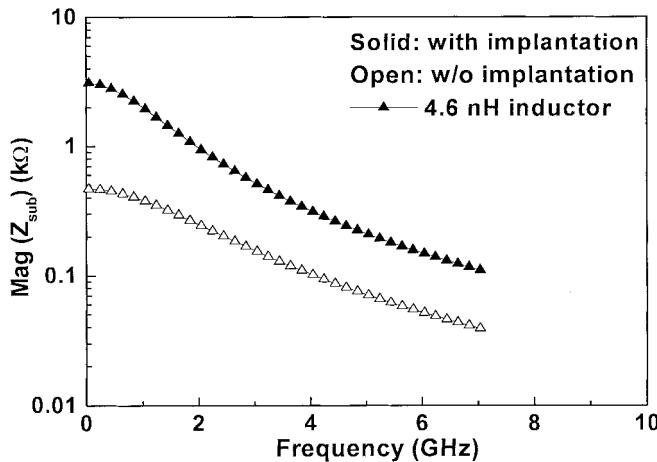

To analyze the RF performance improvement further we have plotted in Fig. 4 the substrate impedance  $|Z_{sub}|$  (parallel  $R_{sub}$  and  $C_{sub}$ ), extracted from the equivalent circuit model, in Fig. 1(b). The substrate impedance is improved by  $\sim$  one order of magnitude, which is also observed in our previous transmission line [4], filter [3] and antenna [5] works. The reduced RF loss of inductor after implantation also explains the improved Q-factor and resonance frequency, shown in Figs. 2 and 3.

Fig. 4. Substrate impedance change before and after the proton implantation.

#### IV. CONCLUSION

Using a proton implantation process applied after inductor fabrication, a large Q-factor improvement of 61% has been obtained in an inductor made in a Si process. Simultaneously the high Q frequency region was extended to 6.2 GHz. This large improvement resulted from the larger substrate impedance. This was determined by extraction from an equivalent circuit model. This simple implantation process shows great potential for high-Q inductors in future applications at high frequencies.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. K. W. Huang of the RF Measurement Laboratory, NDL.

#### REFERENCES

- [1] X. Huo, K. J. Chen, and P. C. H. Chan, "Silicon-based high-Q inductors incorporating electroplated copper and low-k BCB dielectric," *IEEE Electron Device Lett.*, vol. 23, Sept. 2002.

- [2] J. B. Yoon, Y. S. Choi, B. K. Y. Eo, and E. Yoon, "CMOS-compatible surface-micromachined suspended-spiral inductors for multi-GHz silicon RF ICs," *IEEE Electron Device Lett.*, vol. 23, Oct. 2002.

- [3] K. T. Chan, C. Y. Chen, A. Chin, J. C. Hsieh, J. Liu, T. S. Duh, and W. J. Lin, "40-GHz coplanar waveguide bandpass filters on silicon substrate," *IEEE Microwave Wireless Comp. Lett.*, pp. 429–431, Nov. 2002.

- [4] K. T. Chan, A. Chin, C. M. Kwei, D. T. Shien, and W. J. Lin, "Transmission line noise from standard and proton-implanted Si," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 2001, pp. 763–766.

- [5] K. T. Chan, A. Chin, Y. B. Chen, Y.-D. Lin, D. T. S. Duh, and W. J. Lin, "Integrated antennas on Si, proton-implanted Si and Si-on-quartz," in *International Electron Devices Meeting (IEDM) Tech. Dig.*, Washington, DC, Dec. 2001, pp. 903–906.

- [6] Y. H. Wu, A. Chin, K. H. Shih, C. C. Wu, S. C. Pai, C. C. Chi, and C. P. Liao, "RF loss and cross talk on extremely high resistivity (10 K-1M-cm) Si fabricated by ion implantation," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 2000, pp. 241–244.

- [7] Y. H. Wu, A. Chin, K. H. Shih, C. C. Wu, C. P. Liao, S. C. Pai, and C. C. Chi, "The fabrication of very high resistivity Si with low loss and cross talk," *IEEE Electron Device Lett.*, vol. 21, pp. 394–396, 2000.

- [8] Y. H. Wu, A. Chin, C. S. Liang, and C. C. Wu, "The performance limiting factors as RF MOSFET's scaling down," in *Proc. Int. RF-IC Symp.*, June 2000, pp. 151–155.

- [9] A. Chin, K. Lee, B. C. Lin, and S. Horng, "Picosecond photoresponse of carriers in Si ion-implanted Si," *Appl. Phys. Lett.*, vol. 69, pp. 653–656, 1996.

- [10] Y. K. Koutsoyannopoulos and Y. Papanaos, "Systematic analysis and modeling of integrated inductors and transformers in RF IC design," *IEEE Trans. Circuits Syst. II*, vol. 47, no. 8, pp. 699–713, 2000.

- [11] K. B. Ashby, I. A. Koullias, W. C. Finley, J. J. Bastek, and S. Moinian, "High Q inductors for wireless applications in a complementary silicon bipolar process," *IEEE J. Solid-State Circuits*, vol. 31, no. 1, pp. 4–9, 1996.

- [12] C. L. David, L. E. Lawrence, P. Chan, J. Malinowski, H. David, S. Seshu, V. Rich, and C. Michael, "Microwave transformers, inductors, and transmission lines implemented in an Si/SiGe HBT process," *IEEE Trans. Microwave Theory Tech.*, vol. 49, no. 8, pp. 1507–1510, 2001.

- [13] H. Hasegawa, M. Furukawa, and H. Yanai, "Properties of microstrip line on Si-SiO<sub>2</sub> system," *IEEE Trans. Microwave Theory Tech.*, vol. 19, no. 11, pp. 869–881, 1971.

- [14] D. Dubuc, E. Tournier, I. Telliez, T. Parra, C. Boulanger, and J. Grafefeuil, "High quality factor and high self-resonant frequency monolithic inductor for millimeter-wave Si-based IC's," in *IEEE MTT-S Int. Microwave Symp. Dig.*, June 2002, pp. 193–196.